Tuesday, February 17th, 2009

Metrosol has joined SEMATECH’s Front End Process Technologies Program at the College of Nanoscale Science and Engineering (CNSE) of the University at Albany to address metrology and data-analysis solutions for 45nm node and beyond IC fabs. The joint partnership will expand on current work to develop inline metrology techniques to monitor the thickness and composition of high-k (HK) dielectric gate and memory stacks. Metrosol’s vacuum ultraviolet spectroscopic reflectometry (VUV-SR) tool will provide the accurate characterization necessary for inline metrology of advanced logic and memory applications for future technology generations.

“Our VUV-SR technology offers the ability to simultaneously measure thicknesses and compositions of individual layers within the high-k dielectric stacks. Our high throughput provides advanced inline process control capability that allows for greater statistical sampling, more accurate information, and faster problem resolution,” said Kevin Fahey, Metrosol’s CEO.

within the high-k dielectric stacks. Our high throughput provides advanced inline process control capability that allows for greater statistical sampling, more accurate information, and faster problem resolution,” said Kevin Fahey, Metrosol’s CEO.

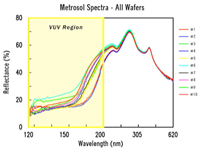

SEMATECH and Metrosol plan to build optical models for interfacial layers, HKMG stacks, and dielectric capping layers, so that reliable thickness and composition measurements may be performed inline using Metrosol’s VUV-SR technology for different logic- and memory-based applications. Metrosol’s VUV system has already been shown to resolve HfSiOx gate dielectric composition independent of thickness (see figure).

“This is another major step in developing practical and inline advanced physical characterization methods to support emerging technologies currently under development in SEMATECH’s Front End Processes program,” said Raj Jammy, SEMATECH vice president of emerging technology. “Metrosol is a strong, trusted partner, and its VUV measurement technology complements our own technical expertise, as we work together to extend CMOS logic and memory technologies.” –E.K.