Tuesday, April 21st, 2009

IMEC has successfully transferred memory variability aware modeling (MemoryVAM), the first EDA tool for statistical memory analysis, to Samsung Electronics. The tool predicts yield loss of embedded SRAMs caused by the process variations of deep-submicron IC technologies. This may be the first proven design-for-manufacturing (DFM) tool to provide statistical analysis across degrees of abstraction from the transistor up to the netlist level. The tool can reportedly avoid design respins by accurately estimating yield losses due to both static and dynamic process variations.

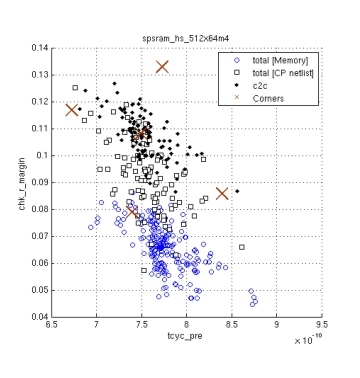

Typical outcome of MemoryVAM for embedded memory, showing preserved correlations for global and local variations of cycle time and read margin for both the CP netlist and the memory. The crosses show a comparison to corner-based simulation. (source: IMEC)

Process variability was in the past defined by corners: boundaries in parameter variation that accounted for process tolerances. However, statistical variations now produce static random phenomena as well as suceptibility to time-dependent variations in supply voltage, temperature, and interference. As can be seen, corners no longer properly bound the functional space (see figure). The world has been waiting for statistical EDA for many years; this may be the foundation of how SoC are designed for the next twenty years.

“This is especially interesting for embedded SRAMs, which are considered to be the most sensitive component to process variations of today’s systems-on-chip,” said Rudy Lauwereins, vice president Smart Systems Technology Office at IMEC. “We are excited that the tool is now being successfully used by the product engineering design teams at Samsung Electronics.”

“We expect that MemoryVAM will be helpful for parametric yield modeling of embedded SRAM design and for understanding the unknown gap between design and silicon results due to process variability in deep sub-micron technology below 45nm,” said Kyu-Myung Choi, vice president of Design Technology Team at Samsung Electronics. Basic information inputs to the tool include transistor-level circuit netlists, memory architectures, and transistor/interconnect variability. More on this in the next BetaSights Newsletter. –E.K.

Tags: 32nm, 45nm, DFM, EDA, eSRAM, IC, process, SRAM, variation, yield