The IC fab industry is notoriously conservative, and normally abstains from risky behavior like contracting new processes. Still, there are times when what we’ve been doing no longer satisfies today’s needs, and we have to try something new. Both Novellus Systems and Applied Materials have recently announced new vapor deposition (VD) tools and integrated process recipes for silicon-oxide dielectrics, after many successful beta-site evaluations by customers. Both technologies create oxide films for 32nm and 22nm node device structures: transistor isolation, various integrated and sacrificial spacers, and sidewall spacer double patterning (SSDP) lithography. Both claim the ability to form “furnace-quality” films, with conformality somewhere between chemical-vapor deposition (CVD) and atomic-layer deposition (ALD).

CFD

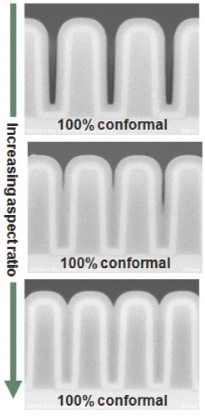

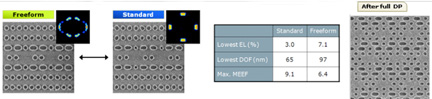

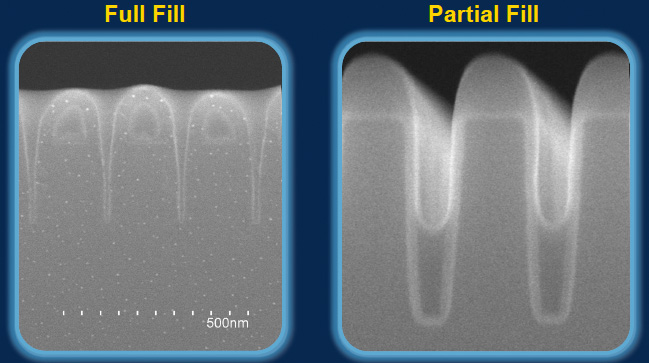

SEM cross-sections of Conformal Film Deposition (CFD) into trenches. (source: Novellus Systems)

Novellus Systems’ multi-station sequential processing (MSSP) PECVD Vector platform gets an upgrade to a new conformal film deposition (CFD) process capability. The company claims 100% step coverage on structures with aspect ratios (AR) of up to 4:1. The company shows SEM cross-sections of ideal trenches for deposition (smooth sidewalls <90°) that are nearly perfectly filled (figure). Such capability could meet 22nm requirements for front-end-of-line (FEOL) applications such as gate liners, spacers, and shallow trench isolation (STI), as well as the spacers that will be used for much of the world’s sidewall spacer double patterning (SSDP) lithography in the future.

CFD technology forms highly conformal films for FEOL applications, doing so at low temperatures to meet the requirements of 22nm node devices. CFD can run <300°C for Flash isolation, and as low as 50°C for direct deposition on photoresist for sidewall spacer double patterning (SSDP) lithography. FTIR spectra and current-voltage plots show that the film behaves like a thermal oxide, and film quality on sidewalls reportedly matches that in the field.

As explained in the recent BetaSights post “Steady as she goes: optical lithography,” due to both delays and projected costs of post-optical lithography, the IC industry is using sidewall spacer double patterning (SSDP) schemes for 32nm node memory and 22nm node logic devices. Applied Materials has been touting the line-width roughness (LWR) healing power of it’s advanced patterning film (APF) for over a year, and so the company would rather deposit the sidewalls onto APF, and APF allows for relatively higher temperature processing. Novellus instead reminds us that the most cost-effective SSDP schemes use a photoresist core.

The thickness range of the CFD film is less than 0.2%, which is <0.1nm on a typical 30nm thick film. “CFD technology offers a breakthrough in the deposition of low temperature dielectric films with quality equivalent to a furnace deposition,” said Kevin Jennings, senior vice president of Novellus’ PECVD Business unit. “As device dimensions shrink beyond 32nm, films deposited using CFD technology will be required for multiple applications.”

Novellus is trying to keep most aspects of the process secret. In response to questions by BetaSights about CFD, the company would only acknowledge that plasma is involved in the process. The precursor is secret, but is “used in semiconductor fabs already,” and there was no exclusive precursors-supplier partner involved in the development.

In comparison to competitive spacer films formed using ALD, Novellus claims that the combination of CFD technology and the Vector MSSD architecture delivers significantly higher throughput and lower chemical consumption. The ALD process of record (POR) for spacers, may be a batch process developed by TEL using furnace ALD intellectual property (IP) acquired from ASM at the end of 2008. The TEL “Telindy Plus” is designed for 32nm node and below IC fabrication, using a 125-wafer batch size and high-speed robotics to oxidize and deposit many different films. The Telindy Plus reportedly handles the ALD step in TEL’s announced quadruple-patterning sidewall spacer lithography flow, though it can also operate in CVD and hybrid CVD/ALD modes for standard SSDP.

FCVD

Applied Materials' “Eterna” flowable CVD (FCVD) dual-chambers, not showing the many sub-system changes from prior PECVD Producer chambers. (source: Business Wire)

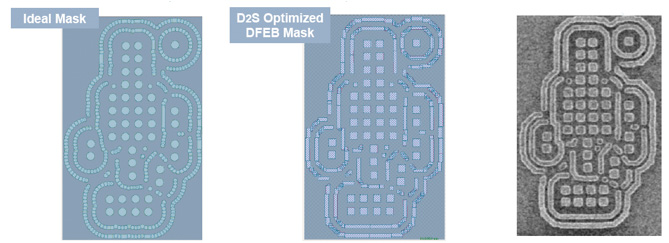

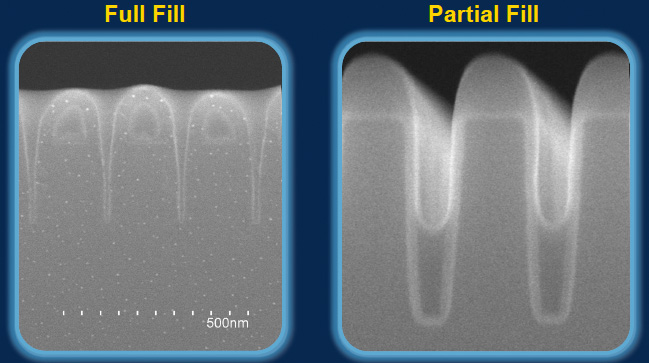

Yesterday, Applied Materials released a flowable CVD (FCVD) process running in new PECVD “Eterna” chambers on the Producer dielectric deposition platform (figure). Targeting 32nm node and beyond ICs with >30:1 AR structures, the FCVD process completely fills gaps from the bottom up with a dense carbon-free silica glass. The FCVD oxide gap-fill process uses secret process chamber sub-systems and a mysterious carbon-free silicon-precursor.

The company says that the chamber had to be significantly re-designed to handle the unique recipe requirements of the precursor and the “flowability.” Standard PECVD chambers reportedly fail in trying to produce FCVD films. “We had to do some unique hardware designs to allows this precursor to go on to the wafer, fill gaps, and leave no carbon in the final film,” said Bill McClintock, Applied Materials’ vice president and general manager of dielectrics and CMP. Consequently, even though it is only matter of time before word leaks out as to which precursor is used, McClintock is confident that OEM competitors will have difficulty in trying to clone the process.

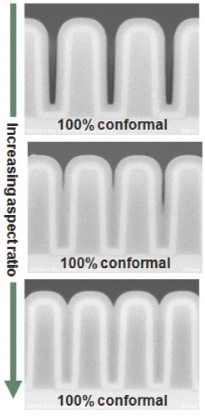

Like Novellus’ CFD silica film, the Applied Materials FCVD silica compares favorably to thermal oxides in terms of density and electrical properties. Unlike the CFD, FCVD is touted as “the ultimate gap-fill dielectric” due to it’s ability to flow into and fill extremely re-entrant structures as narrow as 5nm without voids (figure). Initially targeting DRAM isolation, the FCVD process has past beta-site evaluations at six different end-user fabs for both memory and logic applications. “Every major memory customer has taken one of these,” said McClintock. “They are qualifying them for their major products, whether they be DRAM or NAND.”

Flowable-CVD (FCVD) provides bottom-up gap-filling with silica using a carbon-free precursor. (source: Applied Materials)

For 32nm node processing, the thermal budget for logic is ~400°C while that for NAND Flash is ~300°C. The basic process flow for any gapfill starts with liner deposition, then FCVD or SOG, then anneal(s), then CMP. The main advantage of FCVD over SOG is that a single FCVD anneal step replaces >10 SOG anneal steps. Applied Materials says that the CoO for 32nm node SOG gapfill is ~$20/wafer, with ~$5/wafer from the precursor cost alone. “We’ve worked with the chemical precursor supplier and the material cost per gram is about one-third of the precursor cost of SOG,” said McClintock. However, due to more efficient use of precursors in CVD compared to SOG tools, the actual cost-per-wafer for the FCVD precursor is hinted to be in the US$1.00-1.50 range.

In response to a question regarding the number of FCVD tools needed to support a high-volume fab, the company claimed that for a 22nm node Flash line running 120K wafer-starts-per-month (WSPM) a “couple of tools” would be needed to deposit a desired layer. If we assume 60K WSPM and 30 working days at 20 hours/day, then the throughput for a 6-chamber Producer would be 100 wafers/hour.

Possible FCVD precursors

Trying to pry “proprietary” information out of a technology executive these days is like trying to pull teeth on a roller-coaster: nearly impossible and always awkward. No OEM wants to talk about any real details today. Applied Materials will not say anything about the precursor molecule, oxidizer or possible catalyst used, continuous or pulsed flows, intermediate molecules formed for flowability, or annealing conditions. In private conversation with BetaSights during the official product launch in Santa Clara yesterday, McClintock provides only the single hint that, “The precursor never sees the plasma.”

Company executives have been careful to say that the precursor enters the chamber as a vapor, and initially deposits on the surface in a “liquid-like” manner to provide the great gap-fill. Then plasma is somehow used to transform the flowable material into a solid silica, perhaps in the presence of an oxidizer and/or a catalyst. The Eterna deposition chamber reportedly requires many unique sub-systems and will cost more than other Producer chambers. However, the company claims at least 50% improvement over SOG in terms of CoO for 32nm node and below gapfill.

We may speculate as to possible carbon-free silicon precursors by reviewing the latest catalog of off-the-shelf specialty molecules from established specialty materials suppliers. SAFC Hitech sells both trichlorosilane (“TCS”, SiCl3H) and silicon tetrachloride (“STC”, SiCl4). Air Liquid lists both hexachlorodisilane (“HCDS”, Cl3Si-SiCl3) and trisilylamine (“TSA”, Si3H9N). Online search reveals that Samsung filed for IP on HCDS for low-temperature conformal oxide deposition in 2002, specifying the use of a Lewis Base (such as pyridine or trimethylaluminum) as catalyst and H2O vapor as reactant in a quasi-ALD sequence.

The only thing we know for sure is that Applied Materials claims sole ownership of the FCVD process, and that the process recipe comes free with the purchase of hardware as is standard with industry CapEx terms and conditions. The precursor is commercially available from a single-source today.

Previous FlowFill dielectric

During the Eterna launch event, ever-alert analyst Dean Freeman of Gartner/Dataquest asked about the comparisons between FCVD and the decade-old “FlowFill” dielectric that had been developed by Trikon. What is now part of the STS division of Sumitomo Precision Products (formerly Aviza, formerly Trikon) had failed to launch a flowable CVD dielectric oxide called “FlowFill” that was based on methyl groups. The product claim by Trikon for FlowFill—a “bottoms-up” dielectric fill for device isolation—was nearly identical to the current product claims for Eterna FCVD. The huge difference is that the latter film uses a carbon-free precursor and a more complex recipe to ensure that there is as little carbon as possible left in the final post-annealed material.

Why did FlowFill fail to win over major customers? Siemens reported in 1998 that the material demonstrated reduced reliability compared to SOG. LSI Logic worked with FlowFill, but then became a fabless company and the non-standard unit-process was not picked up but foundries. Perhaps the residual carbon contamination really was excessive, and there was no easy way to anneal it out. Perhaps it was just ahead of it’s time, since FCVD is now touted for 32nm node and below processing there was probably little pull from fabs to replace legacy CVD processes until now.

The future of IC fabrication seems to be more and more based on integrated thin-film depositions and etches (less and less based on simple 2D shrinks). Specialized new tools and materials are being developed to meet the precise needs of high-volume manufacturing. While the capabilities of legacy tools and processes continue to improve, inflection points routinely arise when something completely new suddenly wins the cost:performance tradeoff. With the introduction of CFD and FCVD for oxides, fab process engineers have new tools to use in creating ever more powerful and compact ICs. It is likely that the same tools can be extended to create SiON and SiN films, too. —E.K.